今天小编要和大家分享的是可编程逻辑相关信息,接下来我将从以Flash控制器为核心的FPGA在线更新功能实现设计流程介绍,fpga图像 限时特卖这几个方面来介绍。

可编程逻辑相关技术文章以Flash控制器为核心的FPGA在线更新功能实现设计流程介绍

0 引言

近些年来,由于其灵活可配置性及成本的降低,现场可编程门阵列(Field Programmable Gate Array,FPGA)在嵌入式系统中应用越来越广泛,不论产品的初期研发或是后期维护都不可避免地需要频繁更新FPGA程序。传统的JTAG方式更新FPGA程序的方式是通过开发软件将需固化的文件写入Nor Flash器件。当系统很复杂且需要更新的FPGA数量较多时,JTAG方式更新FPGA程序则费时费力且还需拆结构。若在FPGA内部通过逻辑代码搭建一Flash控制器实现对Flash器件的读写操作,即可并行实现系统内每片FPGA对配置文件的在线更新,大大缩短程序固化时间。本文依托于Xilinx公司的FPGA和Spasion公司的Nor Flash,详细介绍了Flash控制器设计和在线加载功能的实现方法。

1 FPGA配置方式

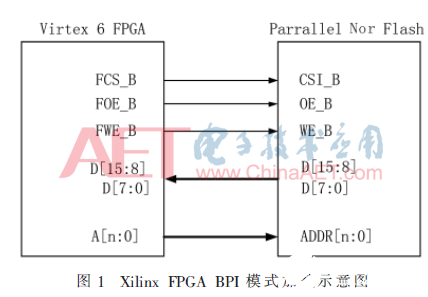

以Xilinx Virtex6 系列FPGA为例,对配置文件的加载方式有串行Flash、并行Flash、JTAG方式等,其中最常用的是并行Flash方式(Byte Peripheral Interface Parallel Flash Mode,BPI),其配置模式如图1所示。

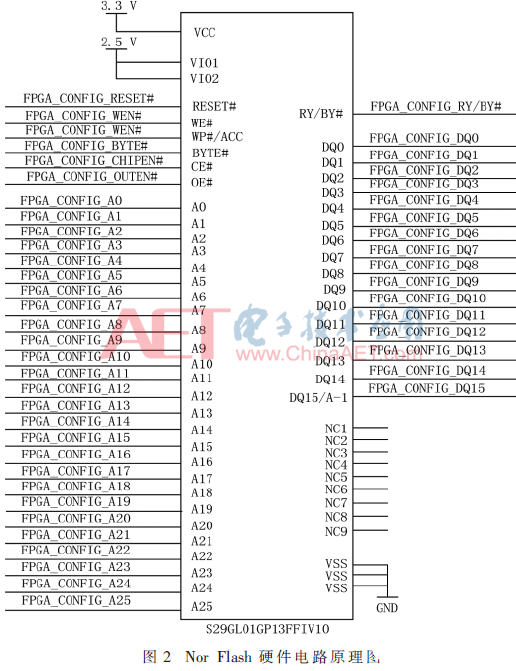

一种实际的FPGA与Nor Flash硬线连接方式如图2所示。

无论是通过JTAG方式还是通过软件操作实现程序更新,都是通过控制这些读写使能信号及地址线实现配置文件的写入,FPGA掉电重启之后再从Flash取出配置数据从而实现加载。本文提出的FPGA在线更新程序的方式则是通过FPGA控制逻辑驱动Flash的数据和地址,从而为多块FPGA并行更新程序的实现提供了前提。

2 Flash控制器设计

Flash器件的基本操作包括读、写、擦除等,这些操作都是通过向相应的命令寄存器写入特定的指令来实现的,这些指令的写入通过操作与FPGA相连的片选信号(ce_n)、写使能信号(we_n)、读使能信号(oe_n)、地址总线(addr[23:0])和数据总线(dq[15:0])实现。